- 您现在的位置:买卖IC网 > Sheet目录366 > TMDXEVM5515 (Texas Instruments)EVAL MODULE DSP FOR C55XX

SPRS645F – AUGUST 2010 – REVISED OCTOBER 2013

2.5.4

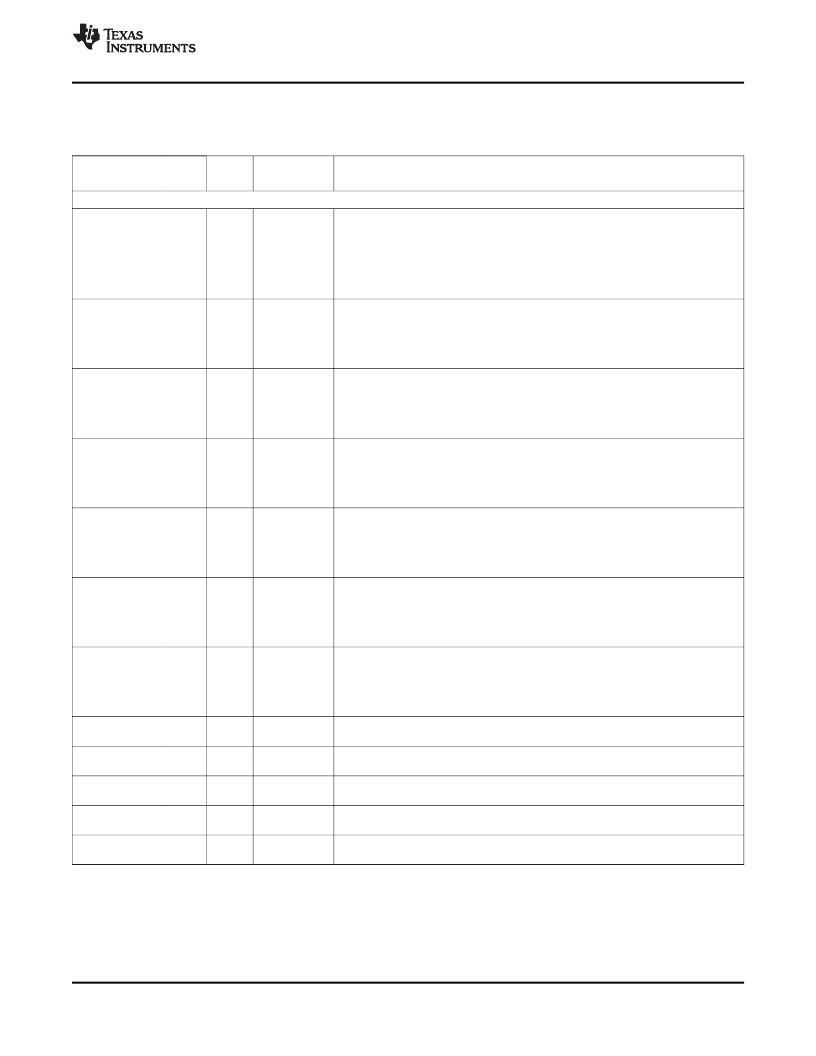

EMIF Terminal Functions

Table 2-8. External Memory Interface (EMIF) Terminal Functions

SIGNAL

NAME

NO.

TYPE (1)

(2)

OTHER (3)

(4)

DESCRIPTION

EMIF FUNCTIONAL PINS: ASYNC (NOR, SRAM, and NAND)

Note: When accessing 8-bit Asynchronous memory:

?

?

Connect EM_A[20:0] to memory address pins [22:2]

Connect EM_BA[1:0] to memory address pins [1:0]

For 16-bit Asynchronous memory:

?

?

Connect EM_A[20:0] to memory address pins [21:1]

Connect EM_BA[1] to memory address pin [0]

This pin is multiplexed between EMIF and GPIO. For EMIF, this pin is the EMIF

IPD

external address pin 20.

EM_A[20]/GP[26]

J3

I/O/Z

DV DDEMIF

BH

Mux control via the A20_MODE bit in the EBSR (see Figure 3-3 ).

The IPD resistor on this pin can be enabled or disabled via the PDINHIBR2 register.

This pin is multiplexed between EMIF and GPIO. For EMIF, this pin is the EMIF

IPD

external address pin 19.

EM_A[19]/GP[25]

G4

I/O/Z

DV DDEMIF

BH

Mux control via the A19_MODE bit in the EBSR (see Figure 3-3 ).

The IPD resistor on this pin can be enabled or disabled via the PDINHIBR2 register.

This pin is multiplexed between EMIF and GPIO. For EMIF, this pin is the EMIF

IPD

external address pin 18.

EM_A[18]/GP[24]

G2

I/O/Z

DV DDEMIF

BH

Mux control via the A18_MODE bit in the EBSR (see Figure 3-3 ).

The IPD resistor on this pin can be enabled or disabled via the PDINHIBR2 register.

This pin is multiplexed between EMIF and GPIO. For EMIF, this pin is the EMIF

IPD

external address pin 17.

EM_A[17]/GP[23]

F2

I/O/Z

DV DDEMIF

BH

Mux control via the A17_MODE bit in the EBSR (see Figure 3-3 ).

The IPD resistor on this pin can be enabled or disabled via the PDINHIBR2 register.

This pin is multiplexed between EMIF and GPIO. For EMIF, this pin is the EMIF

IPD

external address pin 16.

EM_A[16]/GP[22]

E2

I/O/Z

DV DDEMIF

BH

Mux control via the A16_MODE bit in the EBSR (see Figure 3-3 ).

The IPD resistor on this pin can be enabled or disabled via the PDINHIBR2 register.

This pin is multiplexed between EMIF and GPIO. For EMIF, this pin is the EMIF

IPD

external address pin 15.

EM_A[15]/GP[21]

N1

I/O/Z

DV DDEMIF

BH

Mux control via the A15_MODE bit in the EBSR (see Figure 3-3 ).

The IPD resistor on this pin can be enabled or disabled via the PDINHIBR2 register.

EM_A[14]

EM_A[13]

EM_A[12]/(CLE)

EM_A[11]/(ALE)

EM_A[10]

M1

L1

K1

K2

L2

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

DV DDEMIF

BH

DV DDEMIF

BH

DV DDEMIF

BH

DV DDEMIF

BH

DV DDEMIF

BH

This pin is the EMIF external address pin 14.

This pin is the EMIF external address pin 13.

This pin is the EMIF external address pin 12. When interfacing with NAND Flash,

this pin also acts as Command Latch Enable (CLE).

This pin is the EMIF external address pin 11. When interfacing with NAND Flash,

this pin also acts as Address Latch Enable (ALE).

This pin is the EMIF external address pin 10.

(1)

(2)

(3)

(4)

I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal, BH = Bus Holder

Input pins of type I, I/O, and I/O/Z are required to be driven at all times. To achieve the lowest power, these pins must not be allowed to

float. When they are configured as input or high-impedance state, and not driven to a known state, they may cause an excessive IO-

supply current. Prevent this current by externally terminating it or enabling IPD/IPU, if applicable.

IPD = Internal pulldown, IPU = Internal pullup. For more detailed information on pullup/pulldown resistors and situations where external

pullup/pulldown resistors are required, see Section 3.8.1 , Pullup/Pulldown Resistors .

Specifies the operating I/O supply voltage for each signal

Copyright ? 2010–2013, Texas Instruments Incorporated

Product Folder Links: TMS320C5515

Device Overview

21

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TMDXEXP1808L

KIT EXPERIMENTER FOR AM180X

TO263-3EV-VREG

BOARD EVAL TO220-3/TO263-3 VREG

TO263-5EV-VREG

EVAL BOARD VREG TO220-5/TO263-5

TOOLSTICK-EK

KIT TOOL EVAL SYS IN A USB STICK

TPS23757EVM

EVALUATION MODULE FOR TPS23757

TPS62230EVM-370

EVAL MODULE FOR TPS62230-370

TRAVELCUBE

SURGE SUP 1OUT W/RJ11 DIRECTPLUG

TRAVELER100BT

SURGE SUP 2OUT W/RJ11 DIRECTPLUG

相关代理商/技术参数

TMDXEVM5515

制造商:Texas Instruments 功能描述:TMS320C5515 DSP Evaluation Module

TMDXEVM642

制造商:Texas Instruments 功能描述:Tools Development kit For Use

TMDXEVM6424

功能描述:开发板和工具包 - TMS320 C6424 DSP Eval Mod RoHS:否 制造商:Texas Instruments 产品:Experimenter Kits 工具用于评估:F2802x 核心:TMS320 接口类型:UART, USB 工作电源电压:

TMDXEVM6446

制造商:Rochester Electronics LLC 功能描述:DAVINCI EVM BUNDLE W/O EMULATOR - Bulk 制造商:Texas Instruments 功能描述:DAVINCI EVM BUNDLE W/O EMULATOR - Bulk

TMDXEVM6446T

制造商:Texas Instruments 功能描述:DM6446 DIGITAL VIDEO EVALUATION MODULE - Boxed Product (Development Kits)

TMDXEVM6446TS

制造商:Texas Instruments 功能描述:DM6446 DIGITAL VIDEO EVALUATION MODULE - Trays

TMDXEVM6452

功能描述:开发板和工具包 - TMS320 C6452 EVM Evaluation Module RoHS:否 制造商:Texas Instruments 产品:Experimenter Kits 工具用于评估:F2802x 核心:TMS320 接口类型:UART, USB 工作电源电压:

TMDXEVM6455

功能描述:开发板和工具包 - TMS320 C6455 Evaluation Module RoHS:否 制造商:Texas Instruments 产品:Experimenter Kits 工具用于评估:F2802x 核心:TMS320 接口类型:UART, USB 工作电源电压: